APPLICATION

环境振动如何影响芯片良率及系统性解决方案

半导体制造行业对于振动有着极致要求,随着芯片制程进入3nm时代,环境振动控制已成为决定工艺成败的核心因素

1.工艺精度的物理极限

光刻精度需求:EUV光刻机需在硅片上绘制5nm线宽(相当于头发丝的万分之一),要求平台振动位移<1nm RMS。

国际标准等级:SEMIS2/S8规定关键区域需满足VC-E级振动标准(1-80Hz频段振动速度<3μm/s)。

|

工艺环节 |

容许振动速度(μm/s) |

等效位移(nm)| |

|

EUV光刻 |

≤1.5 |

<0.8 |

|

电子束检测 |

≤2.0 |

<1.2 |

|

原子层沉积(ALD) |

≤3.0 |

<2.0 |

|

晶圆切割 |

≤6.0 |

<5.0 |

表一 工艺环节振动要求

注:数据来源2023年SEMI国际标准修订案

二、振动对半导体制造的致命影响

2.1工艺失效

由于厂区环境影响,地面以及其他振动源干扰将会从物理层面直接影响设备精度,导致以下后果

光刻畸变:1Hz/10nm振动导致EUV激光干涉条纹偏移,引发线宽波动超±15%

套刻偏差:3Hz振动使12英寸晶圆产生0.5μrad倾斜,造成层间对准误差≥3nm,

薄膜缺陷:CVD工艺中5Hz振动引起气流扰动,导致薄膜厚度不均性超±8%

2.2 经济损失

除了物理影响外,*直接的影响就是良率下降带来的经济损失。

某5nm晶圆厂实测数据:当2-5Hz振动超标3dB时、良率下降1.8%、损失晶圆1200片、年经济损失超$25M

三、系统性振动解决方案

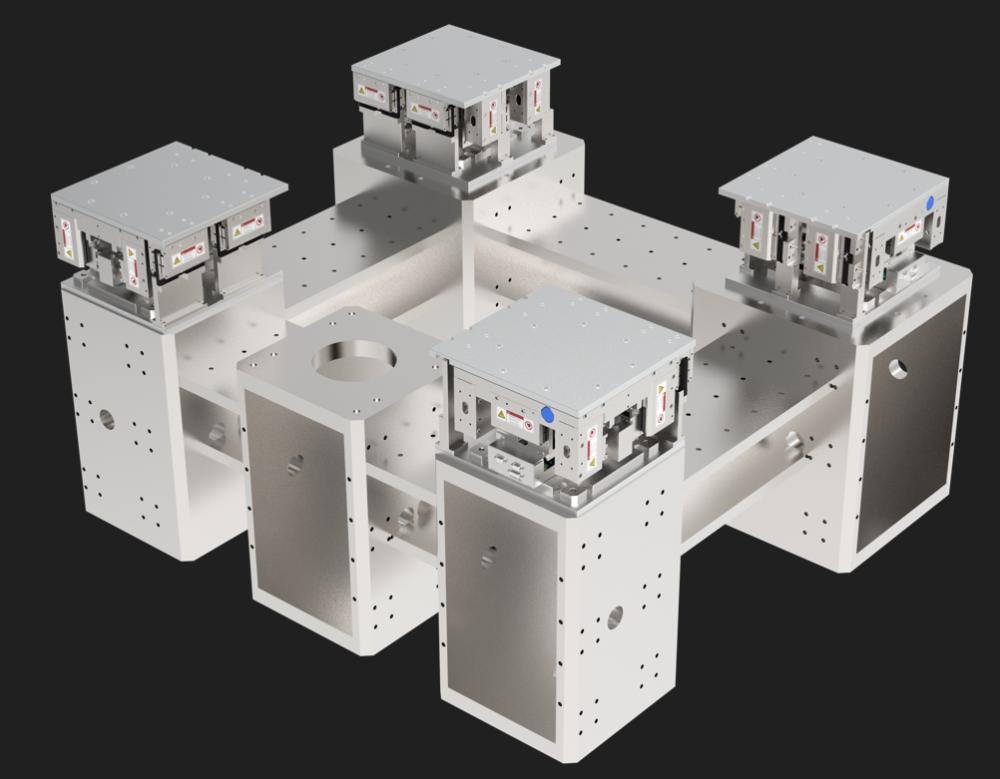

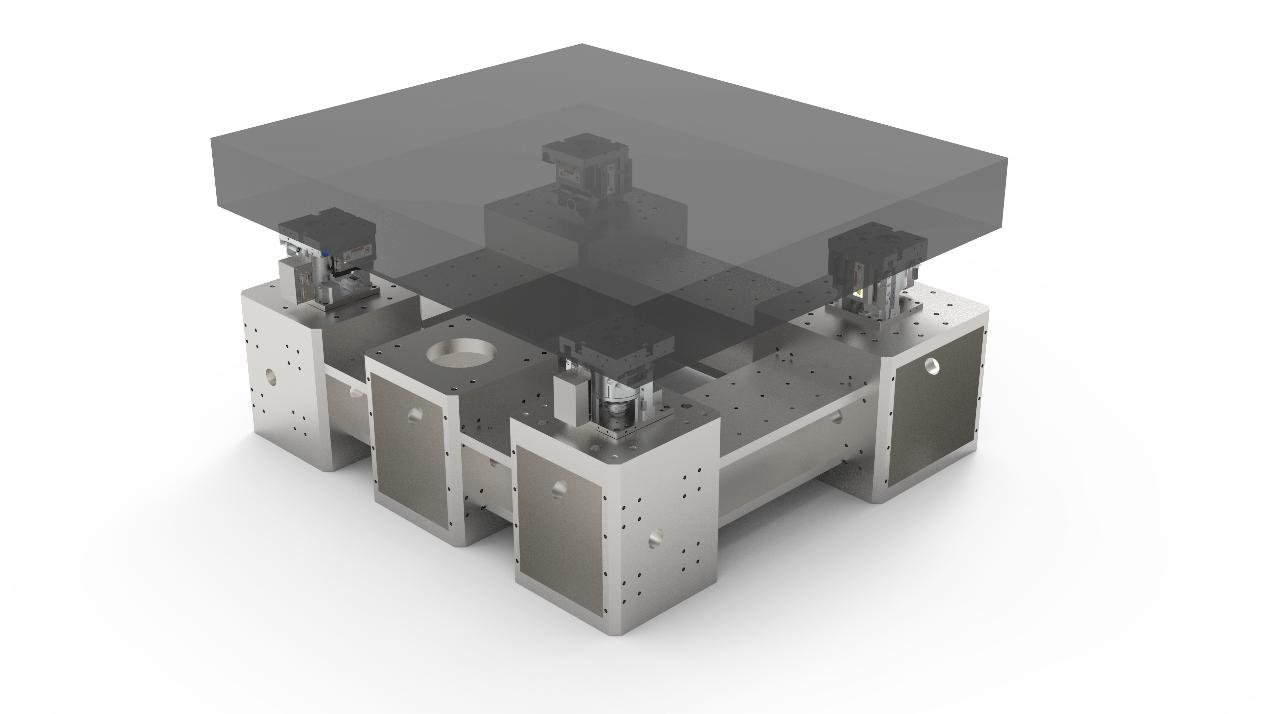

3.1.主动隔振系统核心配置:主动隔振器.

不同于传动被动隔振、主动隔振因其能主动抵消振动,覆盖宽频场景,正逐渐在半导体领域被广泛应用

|

|

主动隔振 |

被动隔振 |

|

自由度控制 |

六自由度 |

三自由度或单自由度 |

|

定位精度 |

纳米级 |

微米级 |

表2 主动隔振系统参数示例

3.2创新技术应用案例

某3nm晶圆厂EUV光刻区受到外部环境影响,导致精度与良率不达标。经过实际测试发现,该厂区在1.6Hz频率有50nm振动,严重影响设备正常运行

解决方案:

安装主动隔振平台(带宽0.5-100Hz)

成效:套刻精度从3.2nm提升至1.5nm、良率提高2.8%、ROI周期<14个月

通过系统性振动控制方案,先进晶圆厂可将环境振动影响降低2-3个数量级,为摩尔定律的持续演进提供基础保障。随着芯片结构进入原子尺度,振动控制能力正成为衡量半导体制造竞争力的关键指标。

四、主动隔振技术带来的行业级提升

|

提升维度 |

主动隔振实现 |

传统被动隔振 |

技术跃迁 |

|

有效隔振频段 |

0.5-200Hz |

>5Hz |

扩展10倍低频能力 |

|

振动控制精度 |

<1nmRMS |

30-50nmRMS |

精度提升2个数量级 |

|

系统响应时间 |

0.1-0.3秒 |

2-5秒 |

提速10倍 |

|

多自由度控制 |

6自由度协同 |

3自由度 |

消除旋转振动影响 |

表3

随着主动隔振器在半导体行业的广泛应用,不同厂商的行业竞争力正在重构。根据2024年行业调研显示:配备先进隔振的晶圆厂、新产品导入周期缩短30%、客户芯片验收良率提升2.1%。领先企业在采用主动隔振系统后,产品精度、良率、产能有了进一步提升,且逐渐拉大了与跟随企业的差距。

|

技术指标 |

领先企业 |

跟随企业 |

差距倍数 |

|

振动控制精度 |

0.6nm |

2.5nm |

4.2x |

|

隔振系统覆盖率 |

100%关键设备 |

40-60% |

1.7x |

|

振动相关良率损失 |

<0.8% |

>2.5% |

3.1x |

表4

主动隔振技术正在引发半导体制造的深层变革:

1. 精度革命:支撑制程向1nm及亚纳米时代迈进

2. 成本重构:将振动相关损失从总成本8%压缩至2%以内

3. 区位解放:颠覆“低振动区建厂”的传统范式

4. 智能底座:成为工业4.0时代晶圆厂的核心数字资产

随着头部企业新建产线配置主动隔振系统,该技术已从“可选配置”升级为“先进制程准入许可证”。在摩尔定律逼近物理极限的当下,纳米级振动控制能力正成为衡量半导体企业核心竞争力的新标尺。

Copyright ? 2020 Zolix .All Rights Reserved 地址:北京市通州区中关村科技园区通州园金桥科技产业基地环科中路16号68号楼B.

ICP备案号:京ICP备05015148号-1

公安备案号:京公网安备11011202003795号

13810146393

13810146393 在线咨询

在线咨询